|

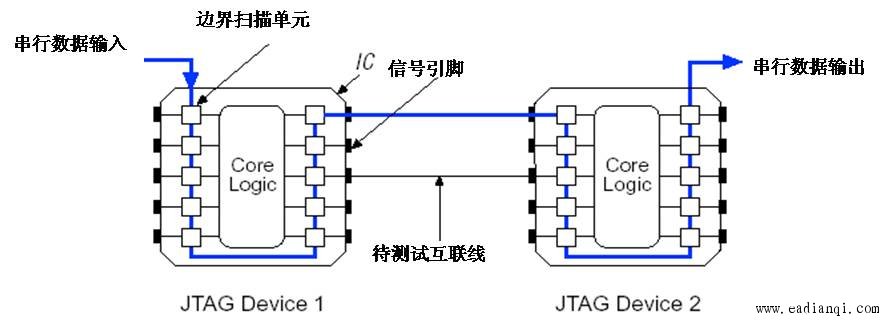

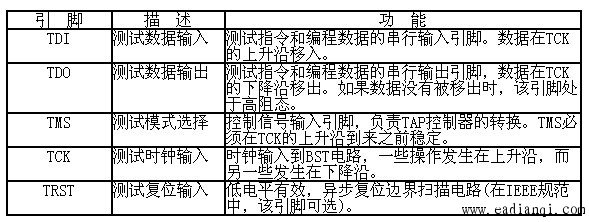

在20世纪八十年代,联合测试行动小组(JTAG,Joint Test Action Group)开发了IEEE1149.1(JTAG)边界扫描测试技术规范。该规范提供了有效的测试引线间隔致密的电路板上的集成电路芯片的能力,主要用于芯片测试和配置等功能。大多数的FPGA厂家遵守IEEE规范,并为输入引脚、输出引脚和专用配置引脚提供边界扫描测试能力。 本文来自www.eadianqi.com  图 边界扫描结构 自动控制网www.eadianqi.com版权所有 该方法提供了一个串行扫描路径,它能捕获器件核心逻辑的内容,或者遵守IEEE规范的器件之间的引脚连接。IEEE 1149.1 标准规定了一个四线串行接口(TDI、TD0、TMS和TCK),及第五条线TRST是可选的,该接口称作测试访问端口 (TAP),用于访问复杂的集成电路 (IC),例如微处理器、DSP、ASIC 和 CPLD 等。边界扫描IO引脚功能如表9.1所示。在TDI(测试数据输入)引线上输入到芯片中的数据存储在指令寄存器中或一个数据寄存器中。串行数据从 TDO(测试数据输出)引线上输出。边界扫描逻辑由TCK(测试时钟)上的信号计时,而且TMS(测试模式选择)信号控制驱动 TAP 控制器的状态。 TRST*(测试重置)是可选项,可作为硬件重置信号,一般不用。 本文来自www.eadianqi.com 表1 边界扫描IO引脚功能 本文来自www.eadianqi.com

低电平有效,异步复位边界扫描电路(在IEEE规范中,该引脚可选)。 |